22C3 - 2.2

22nd Chaos Communication Congress

Private Investigations

| Speakers | |

|---|---|

|

Torsten Hoefler |

| Schedule | |

|---|---|

| Day | 2 |

| Room | Saal 4 |

| Start time | 21:00 |

| Duration | 01:00 |

| Info | |

| ID | 519 |

| Event type | Lecture |

| Track | Hacking |

| Language | English |

| Feedback | |

|---|---|

|

Did you attend this event? Give Feedback |

The Cell Processor

Computing of Tomorrow or Yesterday

The x86 architecture has been the de facto standard for many years. Attempts to take the turn, like Intel tried with the VLIW Itanium Architetcture were desastrous. But the x86 architecture is not able to fulfil the demands of today's market. Several additions have been proposed (MMX,3dNow,SSE1-3), but the Cell approach takes them to the next level.

The cell processor offers unique new features which are focused on high througput computing with low power. This approach is not compatible to the commonly known and widely spread x86 architecture, which survived every attempt to replace it since decades. The latest proposal by Intel, the Itanium architecturue did not make it, they are going to merge back to x86. But the Cell approach is fundamentally different, the aim is not to take the server or workstation market, the architecture is mainly targeted for the console and consumer elektronics.

Two big companies from this sectors, Sony and Toshiba realized a research project together with one of the biggest microprocessor architects, IBM. The result was the Cell architecture, which is in particular very interesting, not only for the consumer electronics but also for the PC, Server and Supercomputing market.

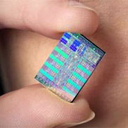

The necessary ideas to implement vector operations additionally to normal operations are also implemented in x86 as MMX/3dNow or SSE1-3, but the Cell architecture has gone further. This architecture proposes a heterogeneous Multiprocessor consisting of a normal general purpose CPU and several (8 in Version 1) small and fast Vector CPUs.

The main concept is to reduce the complexity on the chip to increase the number of functional units and the clock rate. The vector CPUs are cache-less, have no branch prediction scheme and provide only in order execution with two very simple pipelines. All the complexity has been moved inside the upper software layer (compiler), where it can be handled efficiently (cmp. VLIW architectures). All Elements, the computing units and interconnects are introduced and analyzed in the talk. The first prototype with chip layout is explained. Furthermore different (thinkable) programming strategies are shown.